category

摘要:

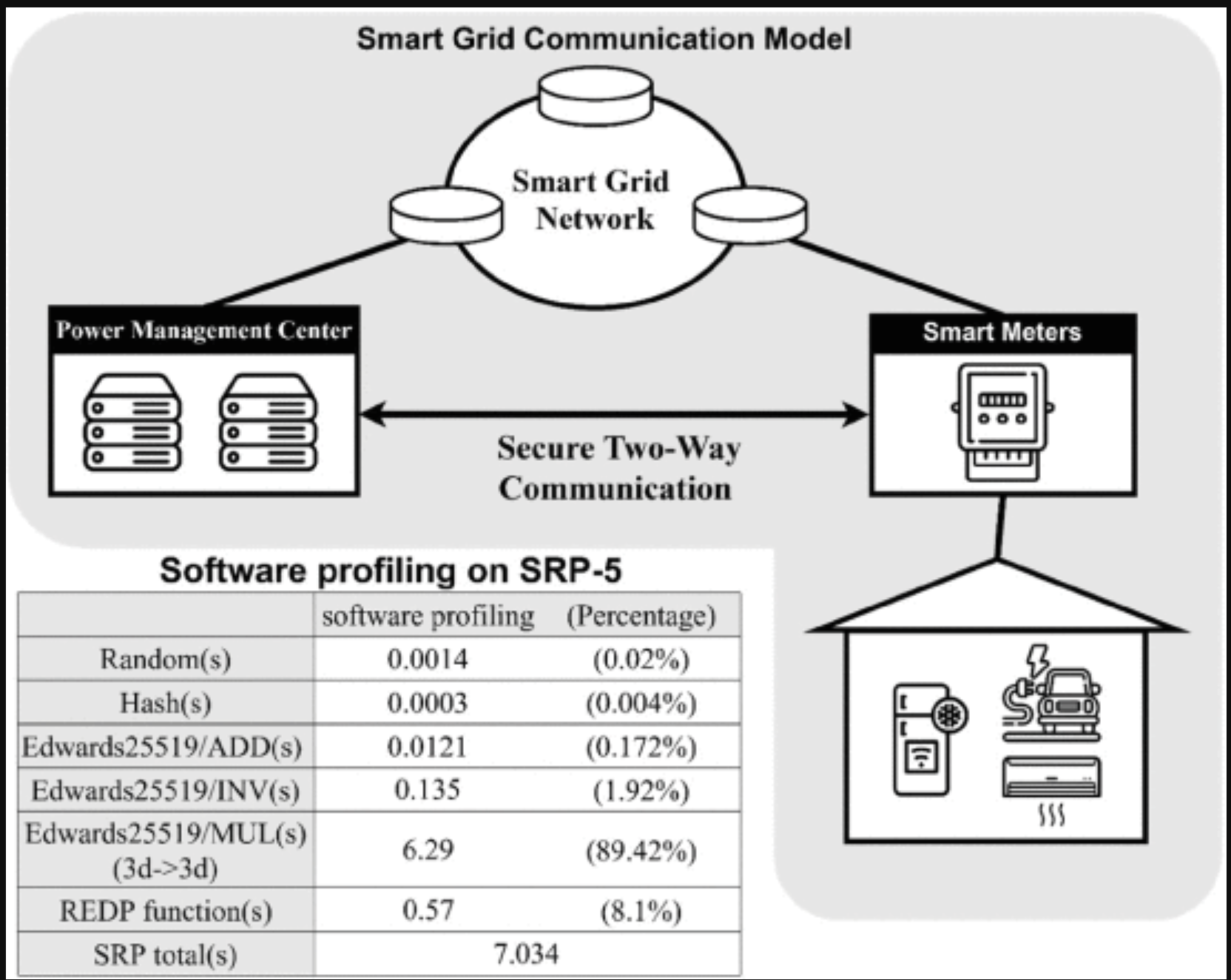

在智能电网中,智能电表将用户的实时数据传输到电力管理中心,而用户则从电力管理中心接收基于时间的定价信息。如图1所示,需要实现安全的双向通信,以便在电源管理中心和智能电表之间通过密钥管理进行相互认证。由于先前采用SRP-3作为智能电网认证步骤的工作[1]在资源约束设备的RSA执行中受到限制,本文提出了一种新的SRP-5[2]密码引擎,其特点是支持椭圆曲线密码术(ECC)和硬件/软件协同设计。

在智能电网中,智能电表将用户的实时数据传输到电力管理中心,而用户则从电力管理中心接收基于时间的定价信息。如图1所示,需要实现安全的双向通信,以便在电源管理中心和智能电表之间通过密钥管理进行相互认证。由于先前采用SRP-3作为智能电网认证步骤的工作[1]在资源约束设备的RSA执行中受到限制,本文提出了一种新的SRP-5[2]密码引擎,其特点是支持椭圆曲线密码术(ECC)和硬件/软件协同设计。

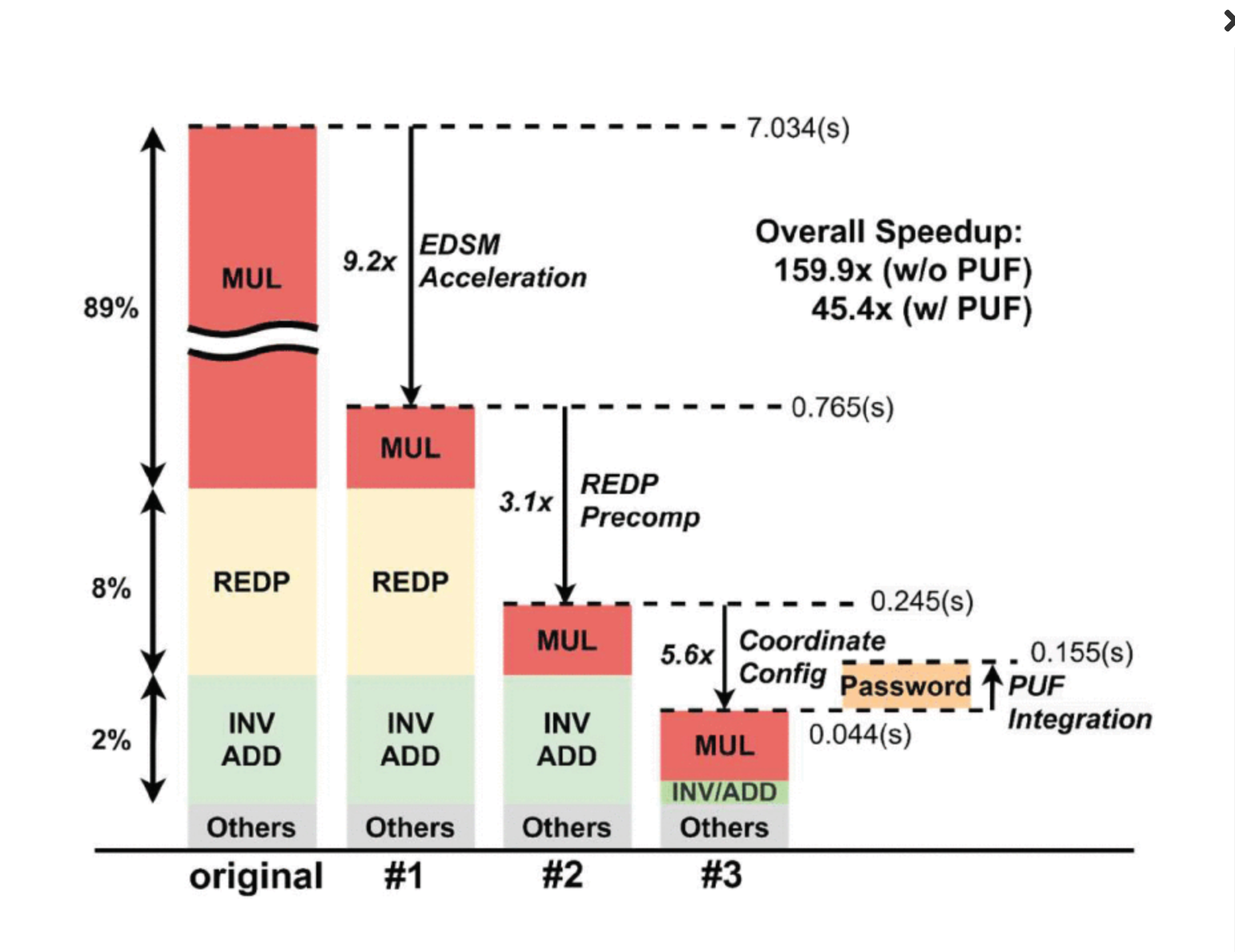

通过在PYNQ-Z2 FPGA平台上对SRP-5的全面分析,该协议的关键时序路径由ECC标量乘法运算(89%)、随机元素推导基元(REDP)计算(8%)和逆运算(2%)组成。这三个操作可以通过EDSM加速、REDP预计算和坐标配置来加速,具体如下。

对于EDSM加速,指定了专门的硬件来加速Edwards25519[3]标量乘法。采用基25.5算法,在素数域算法上将255位数字划分为十个部分,大大减少了计算资源和面积。此外,将曲线点映射到投影坐标系,以完成曲线点加法,而无需素数场求逆,这既费时又易受非恒定执行时间的影响。使用蒙哥马利梯形算法,使标量乘法时间不依赖于密钥,这表明加密时间是恒定的,并且可以防止定时攻击。

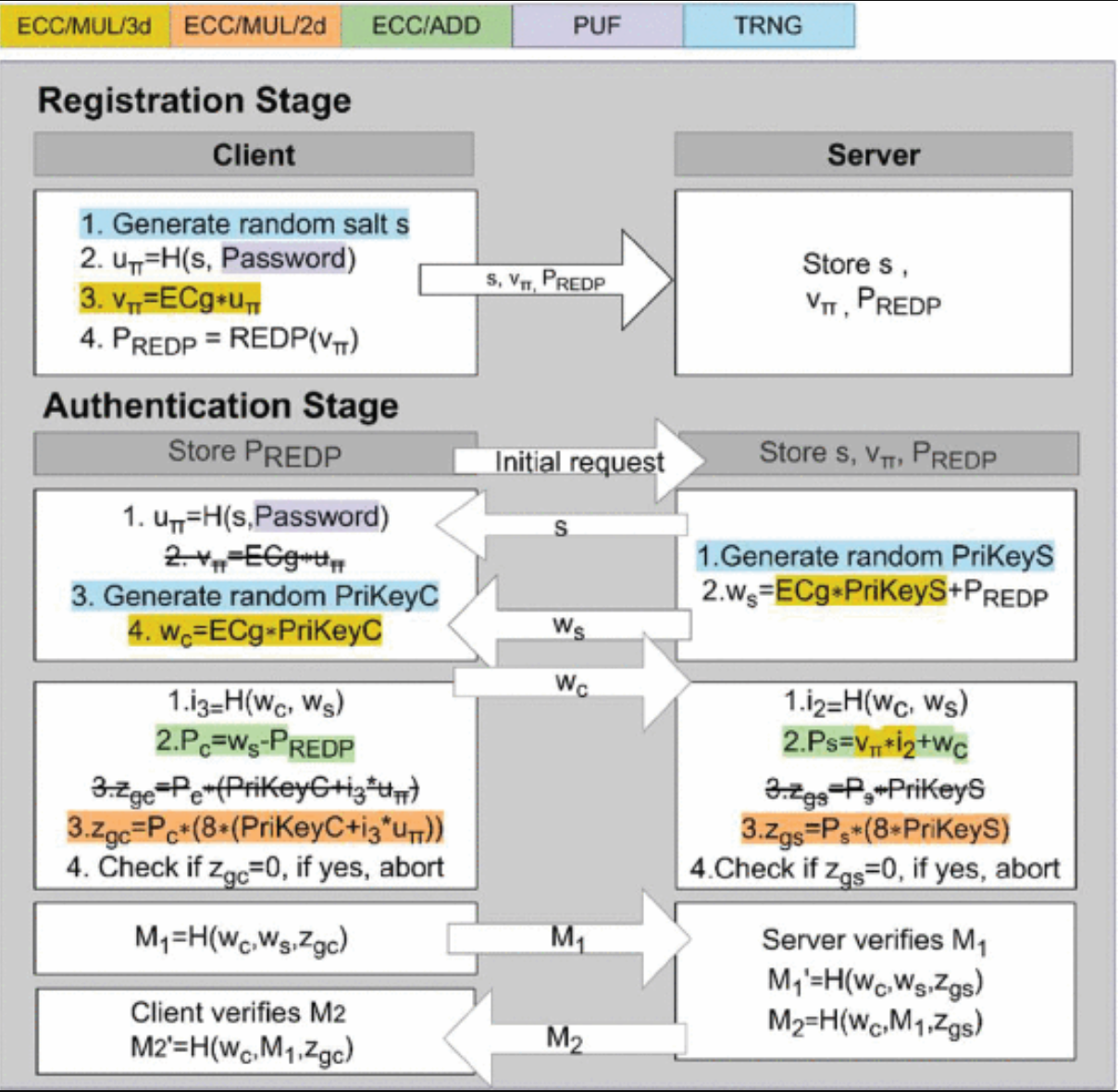

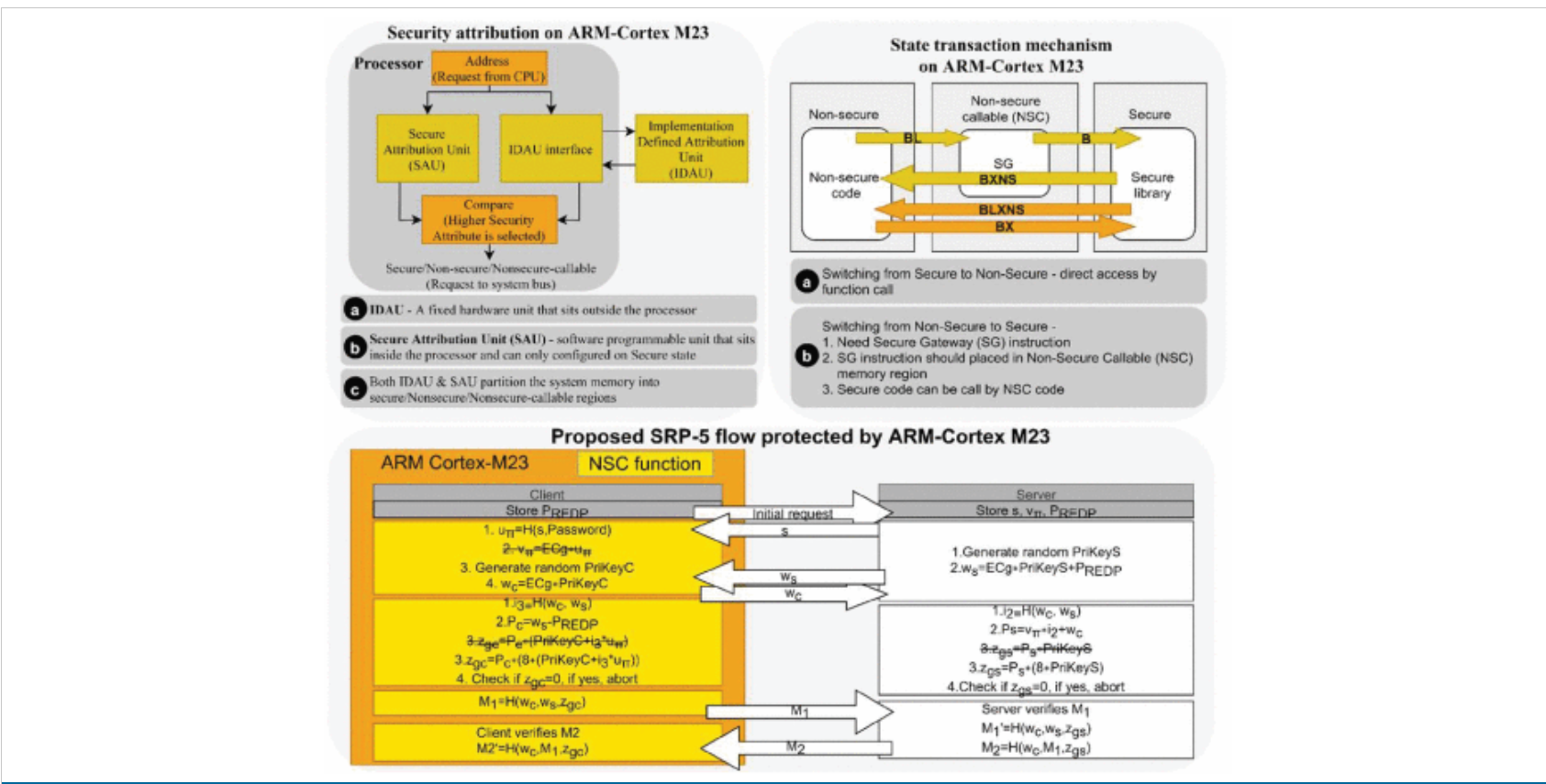

对于REDP预计算,REDP函数可以在椭圆曲线上生成一个随机点。平均而言,需要八次迭代才能找到一个随机的合法点。请注意,每次迭代大约需要14场乘法运算、256场平方运算和一场逆运算。因此,通过将REDP移动到注册阶段,我们可以消除在运行时身份验证时计算REDP函数的成本。此外,客户端不仅消除了REDP计算,还减少了计算验证器v的一个标量乘法,如图2所示。

存储预计算结果的安全性分析如下。客户端和服务器的密钥zgs/zgc都受到PrikeyC/PriKeyS的保护,因此如果攻击者不知道私钥,就无法猜测交换密钥。此外,由于REDP函数受到单向哈希函数的保护,攻击者无法反向计算vπ值。

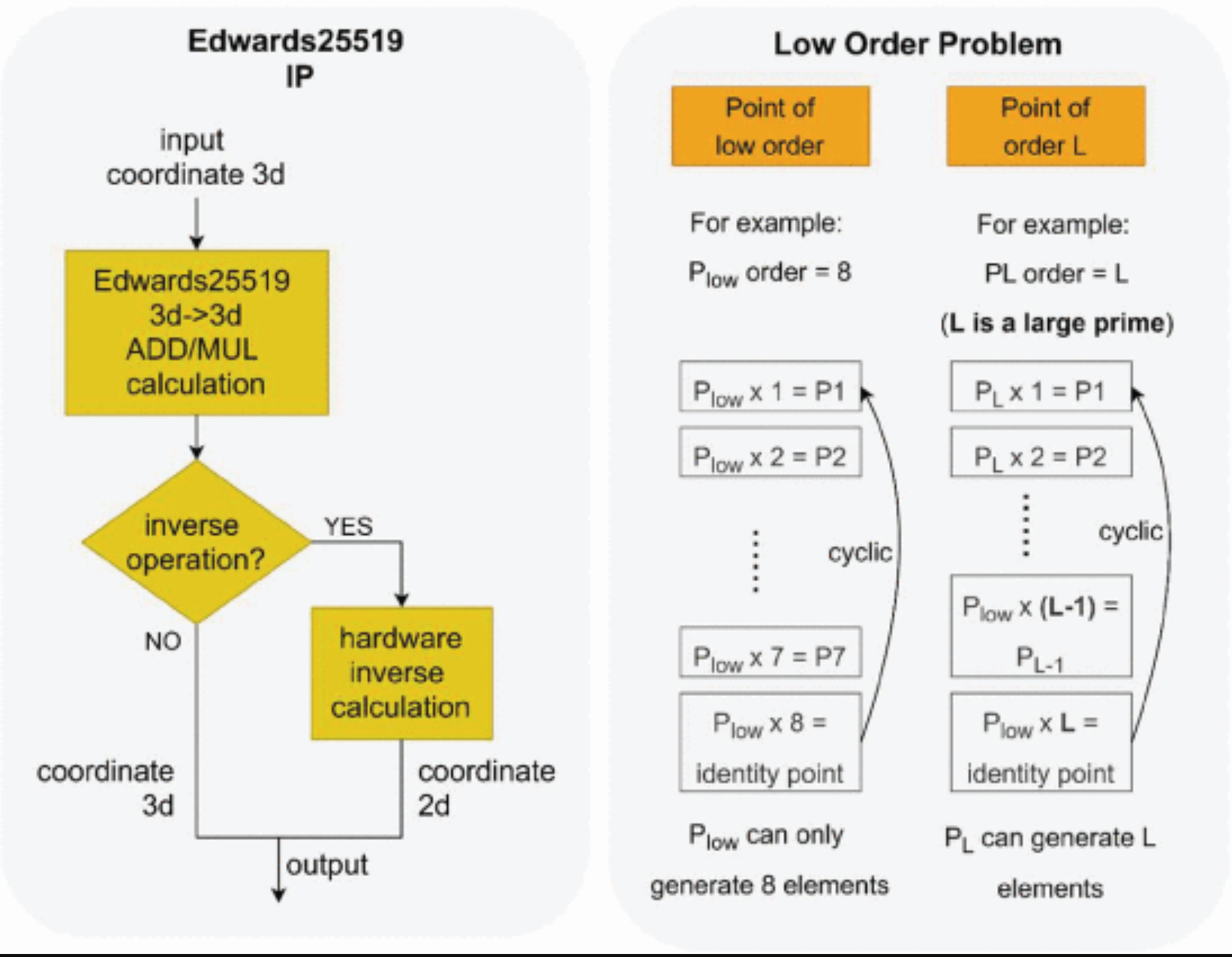

对于坐标配置,我们构建了Edwards 25519 IP,使输出坐标可配置,并可由用户软件选择,以消除反向操作。当将3d点变换为2d时,执行反转操作。虽然曲线点是在项目坐标(3d)中处理的,但我们需要密钥zgs/zgc的仿射坐标(2d)结果来计算哈希函数答案M1/M2。这主要是因为二维坐标中的一个曲线点在三维坐标中可能有多个可能的结果;答案可能不同,并导致身份验证失败。通过坐标配置,处理器无需进行逆操作。逆运算可以从Edwards 25519 IP无缝扩展,因为它可以由原始素数场基函数构造。

除了加速技术之外,还提出了两种额外的方法来提高我们的安全级别——低阶检查和PUF集成。

当椭圆曲线辅因子不为“1”时,会出现低阶问题,导致点的阶数不是L的倍数(子群阶),如图4所示。例如,Edwards25519的辅因子是8,因此Edwards25518上的点只有1、2、4或8阶。该协议将容易受到暴力攻击,因为zgs/zgc点的可能性很小。

低阶检查被广泛用于避免低阶的点目标,它被应用于我们的SRP-5协议,具体来说,是通过用乘8的标量进行标量乘法(将最后3位设置为零),如图3所示。如果结果是曲线上具有素数阶的点,则攻击者无法学习任何东西。然而,如果结果为零,我们可以谨慎地假设攻击者设法迫使点目标Ps/Pc的值处于低位。因此,我们放弃结果并直接停止身份验证。

为了保护密码免受任何类型的攻击,我们将物理不可克隆功能(PUF)[4]集成到PYNQ-Z2系统中,如图4所示。PUF因其高安全性而成为存储我们密钥的合适替代品。PUF板通过其基于PUF的TRNG提供片上PUF数据和随机数。PUF将是我们对密码的信任根,TRNG将是我们的随机源,将用作我们的私钥PrikeyC/PriKeyS。

在FPGA中,接口IP处理PYNQ-Z2和PUF板之间的握手。由于FPGA AXI总线宽度限制,应在Edwards25519 IP和接口IP之前插入串并转换器。采用无效的失效握手来确保IP能够接收正确的输入并将输出存储到适当的存储空间。轮询机制用于检查IP的进度。CPU将持续监控完成寄存器,该寄存器设置为高,表示IP已完成。我们使用轮询而不是中断方法,因为大多数SRP-5操作必须按顺序完成。即使使用中断方法,CPU仍然需要暂停。FPGA的实现观点如图4所示。

图5总结了我们在PYNQ-Z2平台上评估的拟议优化技术。通过EDSM加速,SRP-5的总计算时间将快9.2倍。REDP预计算方法实现了额外的3.1倍加速,坐标配置方法以0.044(s)的计算时间进一步提高了5.6倍。我们集成了PUF板,如图7所示,以增强安全性,尽管存在时间开销。我们的最终计算时间为0.044(s),没有PUF积分,0.155(s)有PUF积分。

图6将这项工作与一系列SRP-3实施进行了比较[5]。这项工作是在采用TSMC 40nm工艺的ARM Cortex M23平台上实现的。Cortex-M23在96MHz时的门计数为220KGE,Edwards25519在952 MHz时为116KGE。估计结果表明,与[5]中的120.77(ms)相比,我们实现了221.2倍的加速,计算时间为5.98(ms)。为了进行安全比较,这项工作在SRP-5中实施,SRP-5比SRP-3更安全。此外,这项工作实现了一个椭圆曲线加速器,支持255位的密钥大小(相当于3072位RSA),而[5]只支持高达2048位的RSA位。

Fig. 1:Smart grid communication model and profiling of SRP-5

Smart grid communication model and profiling of SRP-5

Fig. 2:SRP flow with proposed optimization methods

Smart grid communication model and profiling of SRP-5

Fig. 3:

Coordinate configuration and low order problem on Edwards25519

Coordinate configuration and low order problem on Edwards25519

Fig. 4:Block diagram of the system and FPGA implementation point of view

Fig. 5:

Optimization summary on PYNQ-Z2

Optimization summary on PYNQ-Z2

Fig. 6:

Comparison to prior works

Comparison to prior works

Fig. 7:

Experiment platform on PYNQ-Z2 and PUF

Experiment platform on PYNQ-Z2 and PUF

Fig. S1:

Proposed SRP-5 implemented on ARM-Cortex M23

Proposed SRP-5 implemented on ARM-Cortex M23

Fig. S2:

Edwards 25519 hardware design

Edwards 25519 hardware design

Fig. S3:

Experiment platform and demo video

Experiment platform and demo video

致谢:

这项工作由台湾科技部资助,并获得了科技部1072221-E-009-128-MY3和科技部110-2221-E-A49-157的资助。作者还感谢eMemory和PUFsecurity对PUFrt演示板的支持。

References

- 登录 发表评论

- 29 次浏览

最新内容

- 3 months 1 week ago

- 3 months 1 week ago

- 3 months 1 week ago

- 3 months 1 week ago

- 3 months 1 week ago

- 3 months 1 week ago

- 3 months 1 week ago

- 3 months 1 week ago

- 3 months 1 week ago

- 3 months 1 week ago